# INTERNATIONAL STANDARD

# ISO/IEC 28361

First edition 2007-10-01

Information technology — Telecommunications and information exchange between systems — Near Field Communication Wired Interface (NFC-WI)

Technologies de l'information — Téléinformatique — Interface câblée de communication de champs proche (NFC-WI)

anication de canication de can

ISO LEC

#### PDF disclaimer

This PDF file may contain embedded typefaces. In accordance with Adobe's licensing policy, this file may be printed or viewed but shall not be edited unless the typefaces which are embedded are licensed to and installed on the computer performing the editing. In downloading this file, parties accept therein the responsibility of not infringing Adobe's licensing policy. The ISO Central Secretariat accepts no liability in this area.

Adobe is a trademark of Adobe Systems Incorporated.

Details of the software products used to create this PDF file can be found in the General Info relative to the file; the PDF-creation parameters were optimized for printing. Every care has been taken to ensure that the file is suitable for use by ISO member bodies. In the unlikely event that a problem relating to it is found, please inform the Central Secretariat at the address given below.

ANDARDS 50, COM. Click to view the full Park of SOURC 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURC 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURC 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

ANDARDS 50, COM. Click to View the Full Park of SOURCE 28361. 2007

AND SOURC COPYRIGHT PROTECTED DOCUMENT

#### © ISO/IEC 2007

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Case postale 56 • CH-1211 Geneva 20 Tel. + 41 22 749 01 11 Fax + 41 22 749 09 47 E-mail copyright@iso.org Web www.iso.org

Published in Switzerland

#### **Contents** Page Introduction ......v 1 Scope ...... 1 2 Conventions and notations ......1 3 3.1 Representation of logical states of LOW and HIGH ......1 3.2 3.3 3.4 Symbols and abbreviated terms ...... 2 4 5 6 6.1 6.2 6.3 Clock frequency (f<sub>CLK</sub>)......4 7 Off state ...... 5 7.1 7.2 7.3 De-Activating state .......8 7.4 7.5 Command state 9 8 8.1 Manchester bit coding......10 8.2 8.3 Bit coding for f<sub>CLK</sub>/64 (~212 kb/s)......11 8.4 8.5 Bit coding for fcpk/32 (~424 kb/s) .......12

## **Foreword**

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work. In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC 1.

International Standards are drafted in accordance with the rules given in the ISO/IEC Directives, Part

The main task of the joint technical committee is to prepare International Standards. Draft International Standards adopted by the joint technical committee are circulated to national bodies for voting Publication as an International Standard requires approval by at least 75 % of the national bodies casting a vote.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights

ISO/IEC 28361 was prepared by Ecma International (as ECMA-373) and was adopted, under a special "fast-track procedure", by Joint Technical Committee ISO/IEC JTC 1, Information technology, in parallel with its approval by national bodies of ISO and IEC.

iν

## Introduction

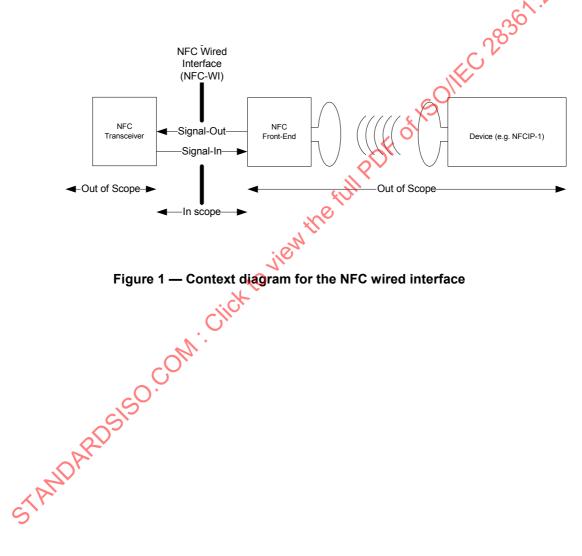

Following the standardisation of Near Field Communication (NFC) systems and their test methods in Ecma International, this International Standard specifies a two-wire interface between two components called "Transceiver" and "Front-end". Systems that implement the NFC-WI interface can thus be augmented with, for example, a wireless Front-end for NFCIP-1 as illustrated in Figure 1. Although this International Standard only specifies requirements for the Signal-In and Signal-Out wires and the digital signals they carry informative Annex A lists some NFCIP-1 specific considerations.

Figure 1 — Context diagram for the NFC wired interface

STANDARDS ISO COM. Click to View the full Policy of the Office 28361-2001

# Information technology — Telecommunications and information exchange between systems — Near Field Communication Wired Interface (NFC-WI)

## 1 Scope

This International Standard specifies the digital wire interface between a Transceiver and a Front-end. The specification includes the signal wires, binary signals, the state diagrams and the bit encodings for three data rates.

#### 2 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

#### 2.1

#### Clock

sequence of LOW and HIGH as defined in 3.2 with duration of  $1/(2*f_{CLK})$ , where  $f_{clk}$  is the clock frequency as defined in 6.3

#### 2.2

#### Information

bit-coded data as defined in Clause 8

#### 2.3

#### Front-end

entity that drives the Signal-Outwire and receives on the Signal-In wire

#### 2.4

#### **Transceiver**

entity that drives the Signal-In wire and receives on the Signal-Out wire

#### 3 Conventions and notations

# 3.1 Representation of bit values

Bit values are either ZERO or ONE.

#### 3.2 Representation of logical states of LOW and HIGH

- The logical signal state is LOW if the electrical level of a signal has the input voltage of V<sub>IL</sub> or the output voltage of V<sub>OL</sub> as specified in Table 1 in 6.2.

- The logical signal state is HIGH if the electrical level of a signal has the input voltage of V<sub>IH</sub> or the output voltage of V<sub>OH</sub> as specified in Table 1 in 6.2.

#### Capitalisation of names

The initial character of names of basic elements, e.g. specific fields, is capitalised.

#### 3.4 State notation

The states are specified in Unified Modelling Language (UML) notation.

# Symbols and abbreviated terms

AND Logical AND operation

fCLK Clock frequency as defined in 6.3

NFC-WI Near Field Communication Wired Interface

OR Logical OR operation

XOR Logical XOR operation

Table 1 in 6.2 list additional symbols for electrical characteristics.

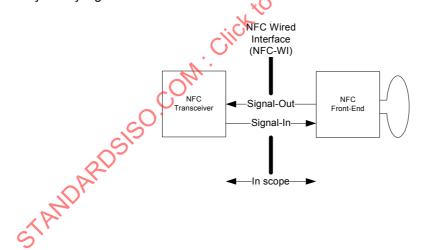

The NFC-Wired Interface (NFC-WI) specifies the Signal in and the Signal-Out wires as illustrated in Figure 2. The wires carry signals of HIGH and LOW.

Figure 2 — NFC-WI

The combinations of the signals on the wires make up the NFC-WI states as defined in Clause 7.

Clause 8 specifies encodings for Information transfer, while in the On state, for the  $f_{CLK}/128$ ,  $f_{CLK}/64$  and f<sub>CLK</sub>/32 data transfer rates.

Annex A lists NFCIP-1 specific considerations for implementing the NFC-WI; Annex B lists possible uses of the Command state, such as changing to alternative protocols.

# 6 Signals

# 6.1 Signal wires

#### 6.1.1 Signal-In

The Transceiver drives the Signal-In wire with a binary signal of HIGH and LOW. The Front-end receives the binary signal on Signal-In.

## 6.1.2 Signal-Out

The Front-end drives the Signal-Out wire with a binary signal of HIGH and LOW. The Transceiver receives the binary signal on Signal-Out.

#### 6.2 Electrical characteristics

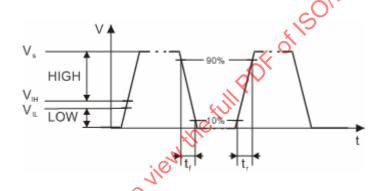

The wires shall carry (binary) digital signals as illustrated in Figure 3 and specified in Table 1.

Figure 3 — Illustration of some electrical parameters

Table 1 — Electrical characteristics

| Symbol             | Parameter                    | Conditions                                                   | Min  | Max  | Unit |  |  |  |

|--------------------|------------------------------|--------------------------------------------------------------|------|------|------|--|--|--|

| DC Characteristics |                              |                                                              |      |      |      |  |  |  |

| V <sub>S</sub>     | Signalling voltage amplitude | Not applicable                                               | 1,62 | 3,63 | V    |  |  |  |

| VIH                | HIGH level input voltage     | Not applicable                                               | 1,10 | 3,63 | ٧    |  |  |  |

| V <sub>IL</sub>    | LOW level input voltage      | Not applicable                                               | 0    | 0,70 | ٧    |  |  |  |

| I <sub>L1</sub>    | Input leakage current        | Input voltage is between $V_{\rm ILmin}$ and $V_{\rm IHmax}$ |      | ± 4  | mA   |  |  |  |

| V <sub>OH</sub>    | HIGH level output voltage    | Driver source current of 4mA                                 | 1,32 | 3,63 | V    |  |  |  |

| $V_{OL}$           | LOW level output voltage     | Driver sink current of 4mA                                   | 0    | 0,30 | V    |  |  |  |

| AC Cha                                                                                                                                                      | racteristics                                                                              |                                                                     |        |      |    |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------|------|----|--|--|--|

| t <sub>r</sub>                                                                                                                                              | Signal-In, Signal-Out rise time (from 10 % to 90 % of $V_{\rm S}$ )                       | Add an external capacitive load between 10 pF and 30 pF for testing | 4      | 20   | ns |  |  |  |

| t <sub>f</sub>                                                                                                                                              | Signal-In, Signal-Out fall time (from 90 % to 10 % of $\rm V_S$ )                         | Add an external capacitive load between 10 pF and 30 pF for testing | 4      | 20   | ns |  |  |  |

| t <sub>SP</sub>                                                                                                                                             | Pulse width of spikes and glitches which must be suppressed by the input filter           |                                                                     |        | 1    | ns |  |  |  |

| C <sub>I</sub>                                                                                                                                              | Input capacitance                                                                         | 1 MHz test frequency                                                |        | 10   | pF |  |  |  |

| C <sub>L</sub>                                                                                                                                              | External load capacitance for the driver                                                  | Not applicable                                                      |        | 30   |    |  |  |  |

| V <sub>ITR</sub>                                                                                                                                            | Input voltage range at signal transitions                                                 | Not applicable                                                      | - 0,30 | 3,93 | V  |  |  |  |

|                                                                                                                                                             | Pulse width                                                                               | Not applicable                                                      | 30     |      | ns |  |  |  |

| Environmental/Test Conditions                                                                                                                               |                                                                                           |                                                                     |        |      |    |  |  |  |

| T <sub>amb</sub>                                                                                                                                            | Ambient temperature for electrical characteristics measurements                           | , 0                                                                 | 20     | 26   | °C |  |  |  |

| Clock frequency (f <sub>CLK</sub> )  clock frequency (f <sub>CLK</sub> ) shall be 13,56 MHz ± 7 kHz.  NFC-WI states  re 4 specifies the main NFC-WI states. |                                                                                           |                                                                     |        |      |    |  |  |  |

| NFC-WI states                                                                                                                                               |                                                                                           |                                                                     |        |      |    |  |  |  |

| re 4 specifies the main NFC-WI states.                                                                                                                      |                                                                                           |                                                                     |        |      |    |  |  |  |

| Off state                                                                                                                                                   | Off state and the On state are the main NEC-WI states. The Off state is the default state |                                                                     |        |      |    |  |  |  |

# Clock frequency (f<sub>CLK</sub>)

The clock frequency (f\_CLK) shall be 13,56 MHz  $\pm$  7 kHz.

## **NFC-WI states**

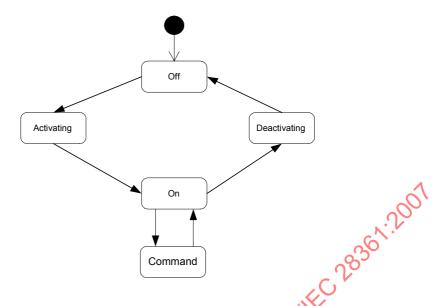

Figure 4 specifies the main NFC-WI states.

The Off state and the On state are the main NFC-WI states. The Off state is the default state.

NFC-WI shall move from the Off state to the On state as specified in 7.2.

NFC-WI shall move from the On state to the Off state as specified in 7.4.

NFC-WI shall move from the On state to the Command state via the Escape sequence.

Figure 4 — Main states of NFC-WI

#### 7.1 Off state

When Signal-In and Signal-Out are LOW for at least 120 µs, the NFC-WI state shall be Off.

NOTE In this state, power saving features may be implemented.

## 7.2 Activating state

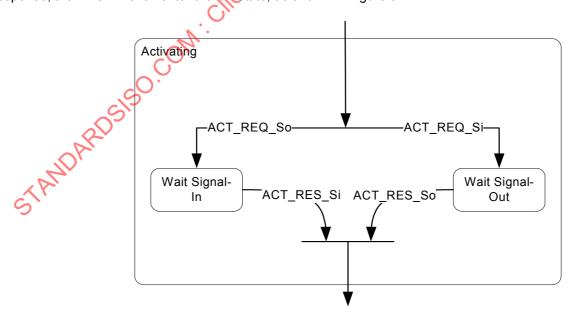

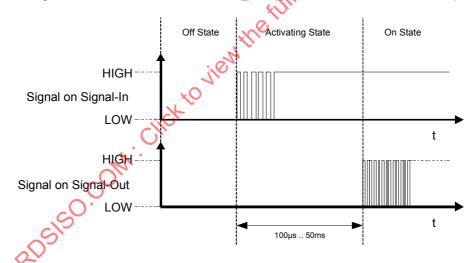

The NFC-WI shall enter the Activating state when either Signal-Out or Signal-In carry the activation sequence, as specified in 7.2.1 and 7.2.2 respectively. When subsequently the opposite wire carries the activation response, the NFC-WI shall enter the On state, as shown in Figure 5.

Figure 5 — Activating state

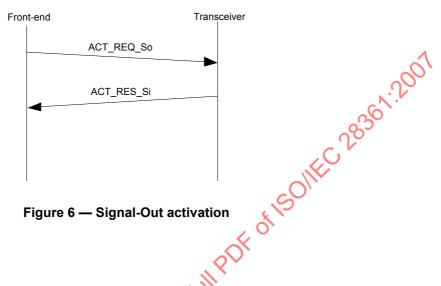

#### 7.2.1 Signal-Out activation

When the Signal-Out wire carries the ACT\_REQ\_So, the NFC-WI shall enter the Activating state. When Signal-In carries the ACT\_RES\_Si no later than 50 ms after entering the Activating state the NFC-WI shall enter the On state. Otherwise the NFC-WI shall enter the Off state.

The activation sequence is illustrated in Figure 6 and Figure 7.

Figure 6 — Signal-Out activation

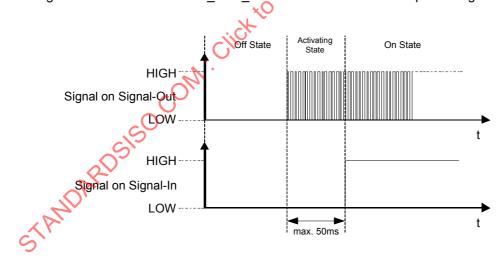

#### 7.2.1.1 ACT\_REQ\_So

The Clock on the Signal-Out wire constitutes the ACT REQ So as illustrated in the upper part of Figure 7.

#### 7.2.1.2 ACT\_RES\_Si

The HIGH on Signal-In constitutes the ACT\_RES\_Si as illustrated in the lower part of Figure 7.

Figure 7 — Signal-Out initiated activation sequence

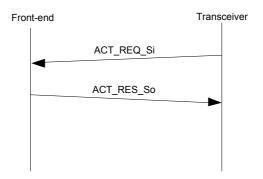

#### 7.2.2 Signal-In activation

When the Signal-In wire carries the ACT REQ Si, the NFC-WI shall enter the Activating state. When Signal-Out carries the ACT\_RES\_So within a period of between 100 µs and 50 ms after entering the Activating state the NFC-WI shall enter the On state. Otherwise the NFC-WI shall enter the Off state.

The activation sequence is illustrated in Figure 8 and Figure 9.

Figure 8 — Signal-In activation

# 7.2.2.1 ACT\_REQ\_Si

At least 127 pulses with a frequency in the range of 2 MHz to 12 MHz on Signal-In constitute the ACT\_REQ\_Si as illustrated in the upper part of Figure 9. Subsequently Signal-In shall be HIGH.

#### 7.2.2.2 ACT\_RES\_So

The Clock on the Signal-Out wire constitutes the ACT\_RES\_So as illustrated in the lower part of Figure 9.

Figure 9 — Signal-In initiated activation sequence

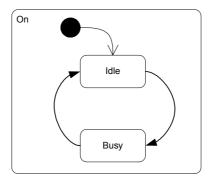

# 7.3 On state

The On state consists of the Idle and Busy sub states; Idle is the default sub-state of On, as shown in Figure 10.

Figure 10 — The On state

#### 7.3.1 Idle

While in the On state, in the absence of Information-transfer, the On sub-state shall be Idle. In the Idle sub-state, Signal-In shall carry HIGH, and Signal-Out shall carry the Clock.

#### 7.3.2 Busy

While in the On state, during Information-transfer on either Signal-In or Signal-Out, the On sub-state shall be Busy.

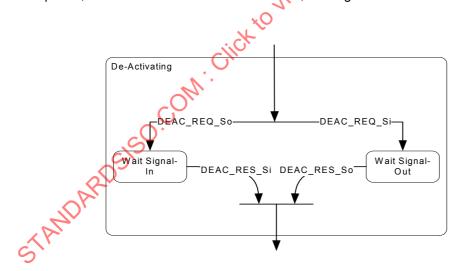

#### 7.4 De-Activating state

The NFC-WI shall enter the De-Activating state when either Signal-Out or Signal-In carry the deactivation sequence as specified in 7.4.1 and 7.4.2 respectively. When subsequently the opposite wire carries the deactivation response, the NFC-WI shall enter the Off state, see Figure 11.

Figure 11 — De-Activating state

#### 7.4.1 Signal-Out deactivation

When Signal-Out carries DEACT\_REQ\_So, the NFC-WI shall enter De-Activating state. Within 50 ms, the Signal-In shall carry DEACT\_RES\_Si, and the NFC-WI shall enter the Off state.

#### 7.4.1.1 DEACT\_REQ\_So

Signal-Out set to LOW for more than 120 µs constitutes the DEACT\_REQ\_So.

#### 7.4.1.2 DEACT\_RES\_Si

Signal-In set to LOW constitutes the DEACT RES Si.

#### 7.4.2 Signal-In deactivation

When Signal-In carries DEACT\_REQ\_Si, the NFC-WI shall enter De-Activating state. Within 50 ms, the 2 of 15011EC 28361.21 Signal-Out shall carry DEACT RES So, and the NFC-WI shall enter the Off state.

#### DEACT\_REQ\_Si 7.4.2.1

Signal-In set to LOW for more than 120 µs constitutes the DEACT REQ Si.

#### 7.4.2.2 DEACT\_RES\_So

Signal-Out set to LOW constitutes the DEACT\_RES\_So.

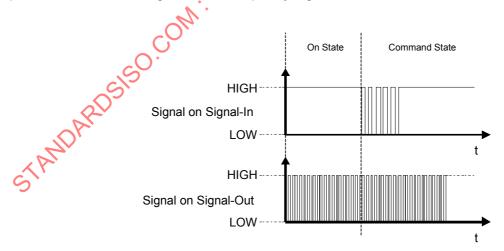

#### 7.5 Command state

The Command state shall be entered from the On state using the Escape sequence. The default bit coding in Command state shall be as defined in 8.3, Bit coding for for 128.

The Command state is exited with a command. The command set is outside the scope of this International Standard.

#### 7.5.1 Escape sequence

At least 127 pulses with a frequency in the range from 2 MHz to 12 MHz on Signal-In constitute the Escape sequence as illustrated in Figure 12. Subsequently Signal-In shall be HIGH.

Figure 12 — Escape sequence

#### Information-transfer 8

This Clause specifies the bit coding for three data rates.

#### Manchester bit coding 8.1

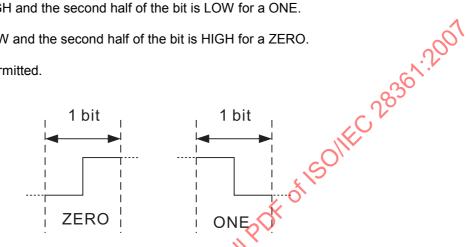

The Manchester bit coding encodes ONE and ZERO in a LOW to HIGH transition in the middle of a bit period as illustrated in Figure 13.

The first half of the bit is HIGH and the second half of the bit is LOW for a ONE.

The first half of the bit is LOW and the second half of the bit is HIGH for a ZERO.

Reverse polarity shall be permitted.

Figure 13 — Manchester bit coding

#### **Modified Miller bit coding** 8.2

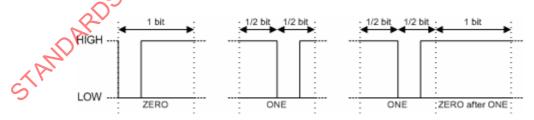

The Modified Miller bit coding defines ONE and ZERO by the position of a pulse during one bit period. The pulse is a transition from HIGH to LOW, followed by a period of LOW, followed by a transition to HIGH. The bit representation is illustrated in Figure 14.

For a ONE the pulse shall occur in the second half of the bit period; the transition from HIGH to LOW shall be in the middle of the bit period.

For a ZERO a pulse shall occur at the beginning of the bit period with the following exception. In case a ZERO bit follows a ONE bit, no pulse shall occur during this ZERO.

Figure 14 — Modified Miller bit coding

The jitter margin for the rising pulse edge is +/- 2/fc.

NOTE For implementation recommendations the propagation delays as specified in A.3 should be respected.

# 8.3 Bit coding for $f_{CLK}/128$ (~106 kb/s)

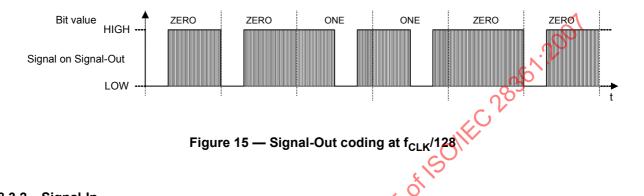

## 8.3.1 Signal-Out

Signal-Out shall carry the AND combination of the Modified Miller bit coded data and  $f_{\mbox{\scriptsize CLK}}$  as illustrated in Figure 15.

The Modified Miller bit coded pulse is at least 7 and at most 45 f<sub>CLK</sub> cycles long.

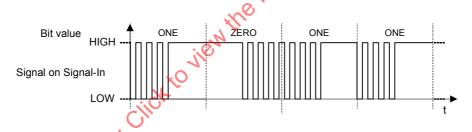

#### 8.3.2 Signal-In

Coding on Signal-In shall carry the OR combination of the inverted Manchester bit-coded data and (f<sub>CLK</sub>÷16). Every bit shall start with the low phase of the (f<sub>CLK</sub>÷16) as illustrated in Figure 16.

Figure 16 — Signal-In coding at f<sub>CLK</sub>/128

# Bit coding for f<sub>CLK</sub>/64 (~212 kb/s)

#### 8.4.1 Signal-Out

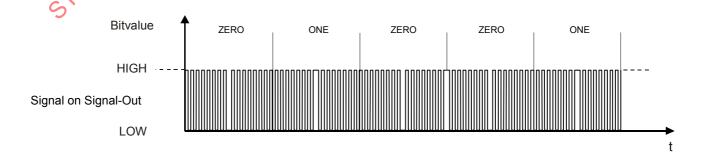

Signal-Out shall carry the XOR of the Manchester bit-coded data and the Clock, as illustrated in Figure 17.

Figure 17 — Signal-Out coding at f<sub>CLK</sub>/64

#### 8.4.2 Signal-In

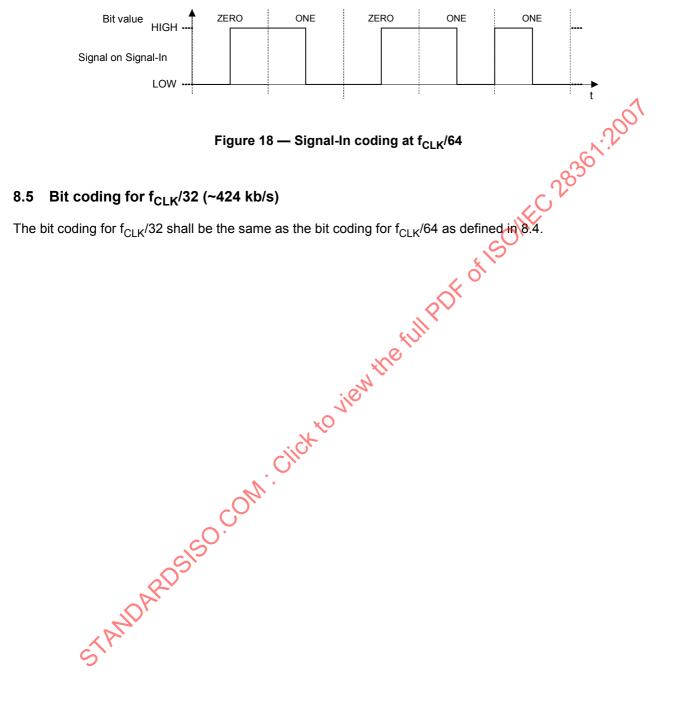

Coding on Signal-In shall carry the Manchester bit-coded data, as illustrated in Figure 18.

# Annex A (informative)

# Application of NFC-WI with NFCIP-1

#### A.1 General

This Annex list specific considerations for NFCIP-1 devices that implement NFC-WI.

#### A.2 Reference

ISO/IEC 18092, Information technology — Telecommunications and information exchange between systems — Near Field Communication — Interface and Protocol (NFCIP-1)

## A.3 Propagation delay

The propagation delay of the Front-end is the integer number of clock cycles needed for signal processing in the Front-end. This delay is divided into two parts, one time for Signal-Out  $(t_1)$  and one for Signal-In  $(t_2)$ . The sum of them is the propagation delay.

ISO/IEC 18092 Front-ends, using the NFC-WI interface have the following requirements on the propagation delay:

For data rate  $f_{Cl K}/128$ :  $(t_1 + t_2)$  equal to 128 clock cycles

For data rate  $f_{CLK}/64$ :  $(t_1 + t_2)$  maximum 256 clock cycles

For data rate  $f_{CLK}/32$ :  $(t_1 + t_2)$  maximum 256 clock cycles

#### A.4 Communication mode

The default communication mode is the Passive communication mode.

#### A.5 RF-field control during activation

In 72, this International Standard defines the Activating state.

The activation sequence defined in 7.2.2 only activates the NFC-WI. Whether the NFCIP-1 RF-field is switched on is described by the following two cases.

#### A.5.1 Activation without RF-field

When ACT\_REQ\_Si is shorter than 100µs the NFC-WI enters the On state without the Front-end switching on the RF-field.